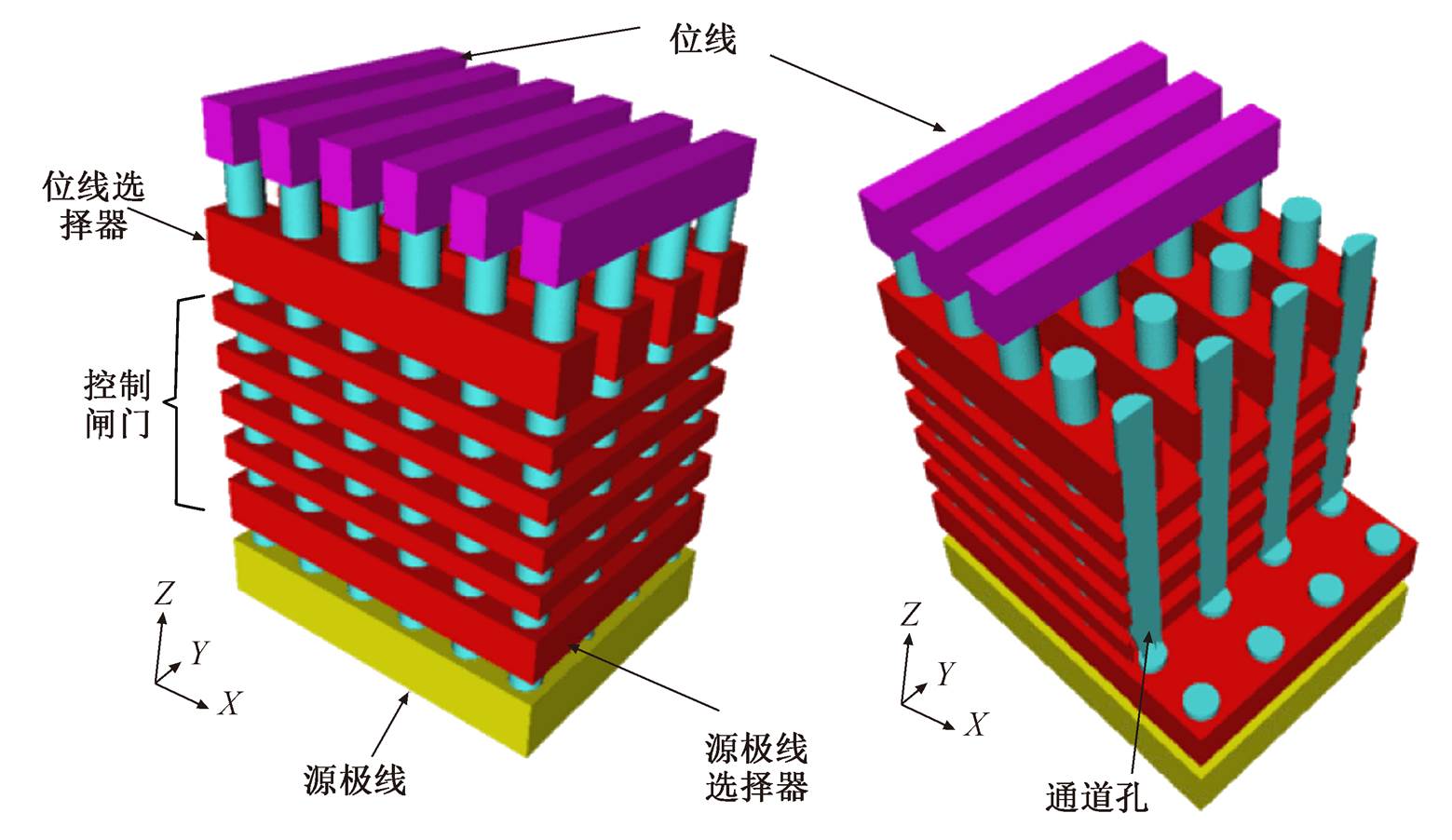

图1 3D NAND结构[3]

Fig. 1 3D NAND structure[3]

摘要 由于常规等离子体刻蚀系统在晶圆边缘处的阻抗与晶圆中心处的阻抗不一致, 使离子在晶圆边缘处的运动轨迹发生偏移, 很难满足越来越高的刻蚀工艺均匀性及深宽比的要求。本文提出一种通过调整晶圆边缘阻抗进行边缘离子运动方向优化的方法, 可以连续实时地调整边缘离子的运动轨迹, 实现对边缘离子运动方向的控制。研究结果表明, 离子的运动方向可以被优化为垂直于晶圆表面, 从而能获得良好的刻蚀速率均匀性及垂直的刻蚀形貌。

关键词 等离子体刻蚀; 3D NAND; 离子运动轨迹; 边缘阻抗; 刻蚀均匀性

随着硅基集成电路技术遵循摩尔定律向更小尺度发展[1-2], 在晶圆(wafer)边缘的晶体管数目越来越多, 因此, 对晶圆边缘刻蚀工艺的优化也越来越重要。近些年广泛应用的立体堆叠闪存(3D NAND)工艺结构(图 1)中, 其较高的工艺均匀性及刻蚀深宽比的要求, 使得对等离子体边缘鞘层以及离子运动轨迹控制的需求日益突出。高深宽比通道孔(channel)蚀刻是 3DNAND 工艺中最重要、最具挑战性的步骤之一, 也是在堆叠层上均匀打孔并形成存储单元通道的关键环节[4]。这一刻蚀工艺需要精确地控制蚀刻离子运动的能量和方向, 以获得垂直且上下孔径一致的刻蚀通孔, 要求等离子刻蚀设备具备先进的等离子约束及调制能力。

对于等离子体刻蚀设备, 晶圆边缘的电性不连续导致等离子体鞘层(sheath profile)在晶片边缘发生畸变, 晶圆边缘等离子体的运动轨迹出现偏移。Babaeva 等[5]模拟了聚焦环(Focus Ring)的高度和电性对离子能量和运动轨迹的影响。Denpoh 等[6]报道了晶圆片边缘附近离子轨迹的畸变。Vincent 等[7]认为优化聚焦环结构可以提高晶圆边缘处刻蚀的均匀性。Ishikawa 等[8]指出聚焦环在调整晶圆边缘鞘层轮廓以及保持等离子体均匀性方面有非常重要的作用, 入射离子的运动轨迹受鞘层控制, 而鞘层由等离子体与聚焦环的耦合决定。因此, 适当的聚焦环设计可以实现晶圆边缘垂直的入射离子角度。然而, 在刻蚀设备的一个维护周期中, 随着晶圆边缘聚焦环逐渐消耗, 晶圆边缘处等离子体鞘层和离子运动的方向会出现一定程度的扭曲和偏转, 导致不均匀刻蚀的产生。因此, 为了获得良好的器件性能, 在规模量产中如何控制边缘刻蚀的均匀性成为这一领域中亟待解决的问题。

图1 3D NAND结构[3]

Fig. 1 3D NAND structure[3]

针对这一问题, 国外刻蚀设备公司提出采用可上下移动的聚焦环[9]。这种设计可以不断地提升聚焦环的位置, 适时地弥补边缘等离子体鞘层的畸变, 优化边缘离子运动的轨迹。但是, 这种设计成本较高, 并且由于在晶圆边缘引入可升降的装置, 可能带来颗粒污染及在移动过程中聚焦环偏离中心的新问题, 且这一设计在工艺进行中不可以实时调节。

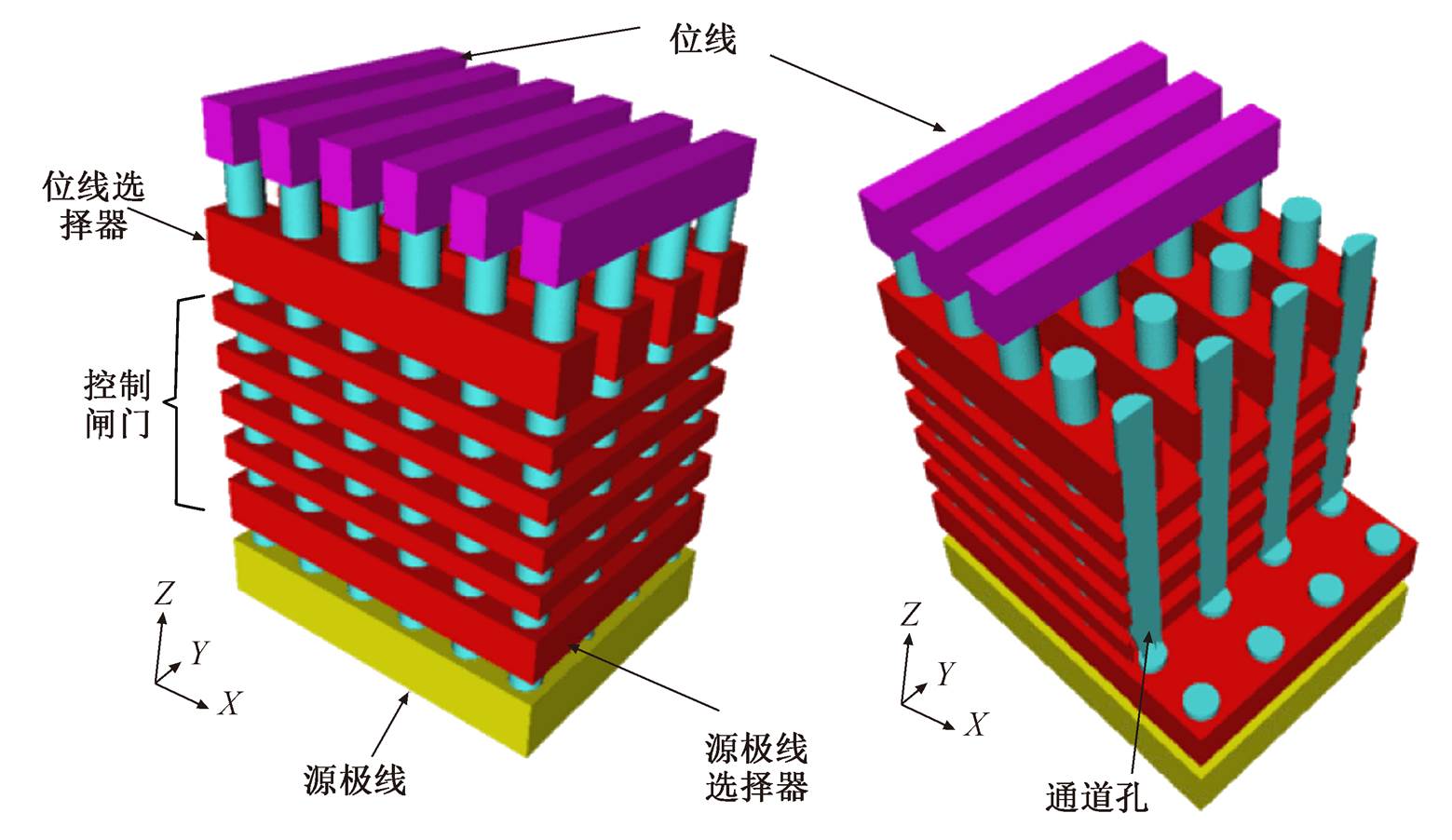

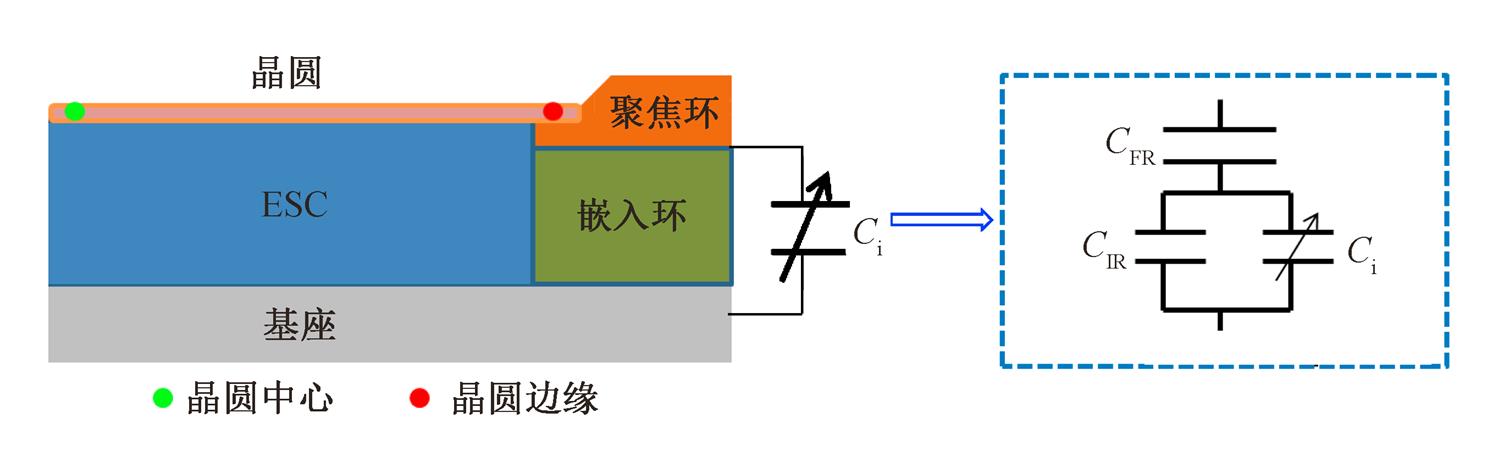

本文在晶圆边缘区域引入一个可以调节大小的边缘电容, 利用这个可变电容来调整边缘区域的阻抗, 进而影响晶圆边缘区域的等离子体的耦合量, 达到控制边缘离子运动轨迹和能量的目的。通过这种方法, 可以实时调整边缘离子的入射方向, 且没有需要上下移动的部件, 不会引入颗粒污染等问题。

我们通过实验, 测量在不同阻抗下氧化硅晶片的刻蚀速率, 并在 3D-Nand ACL 工艺刻蚀过程中, 验证不同边缘阻抗对离子运动轨迹的影响。通过进一步优化晶圆边缘阻抗, 获得垂直的刻蚀形貌。利用 ESI 公司 CFD-ACE 软件的等离子体流体模型, 模拟不同晶圆边缘阻抗对等离子体耦合、鞘层以及离子运动方向的影响。实验中使用的刻蚀机是中微半导体公司自主开发的 ICP Primo-Nanova 12 英寸(300 mm)电感耦合等离子体硅刻蚀机。如图 2 所示, 在晶圆边缘区域引入一个可以调节大小的边缘电容。

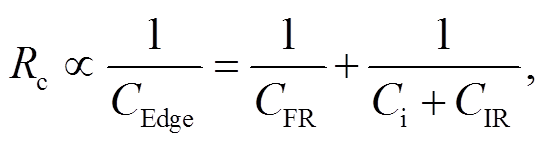

引入可变电容后, 边缘的总阻抗 Rc 可以表示为

图2 边缘引入可变电容的示意图及等效电容图

Fig. 2 Schematic and equivalent capacitance diagram of variable capacitance at wafer edge

其中, Cedge是边缘的总电容, CFR是聚焦环的电容, CIR是嵌入环的电容, Ci是可变电容。由上式可以看出, 调节可变电容 Ci的大小可以改变晶圆边缘区域的阻抗。边缘阻抗进一步影响决定耦合到边缘区域射频功率量, 从而控制边缘区域刻蚀速率及离子运动方向。

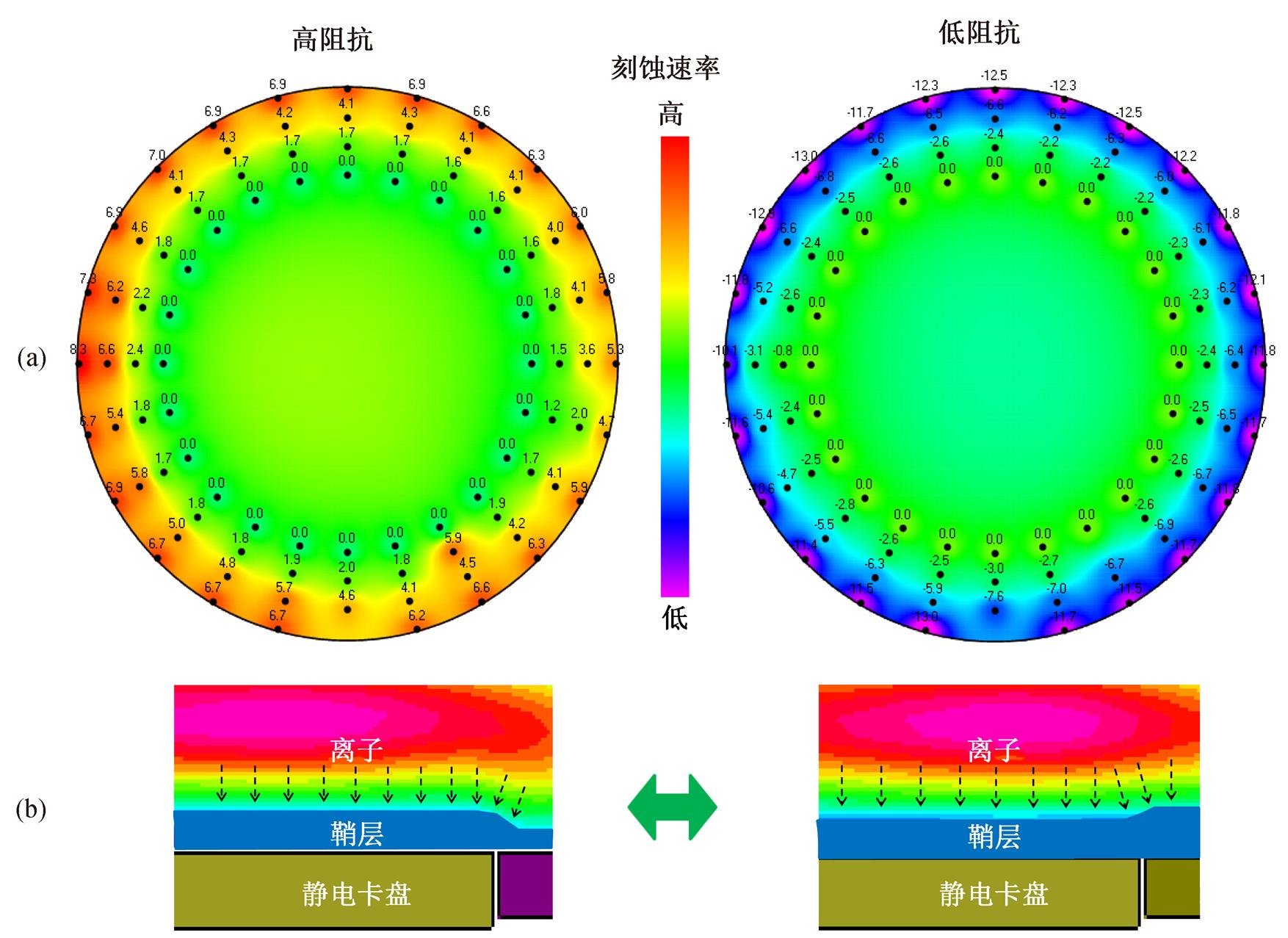

刻蚀速率图中数据点的坐标半径分别为146, 147, 148和149 mm

图3 不同阻抗条件的边缘氧化硅刻蚀速率图(a)以及不同阻抗下鞘层形状及等离子体运动方向的模拟结果(b)

Fig. 3 Etch rate map of oxide at wafer edge under different impedance (a) and the simulation results of the shape of the sheath layer and the direction of ion track under different impedance (b)

图 3 显示由可变电容调整的高、低阻抗(high/ low impedance)下氧化硅的刻蚀速率图。当可变电容设置为高阻抗时, 会将较低的射频功率耦合到聚焦环区域, 减小边缘区域等离子鞘层区的厚度, 边缘鞘层轮廓发生畸变, 更多的离子轰击到晶片边缘而不是聚焦环组件。因此, 随着边缘阻抗的增加, 晶片边缘的刻蚀速率增加。反之, 当可变电容设置为低阻抗时, 会将较高的射频功率耦合到聚焦环区域, 增加边缘区域等离子鞘层区的厚度, 更多的离子轰击到聚焦环组件而不是晶片边缘。因此, 随着边缘阻抗的减少, 晶片边缘的刻蚀速率减小。

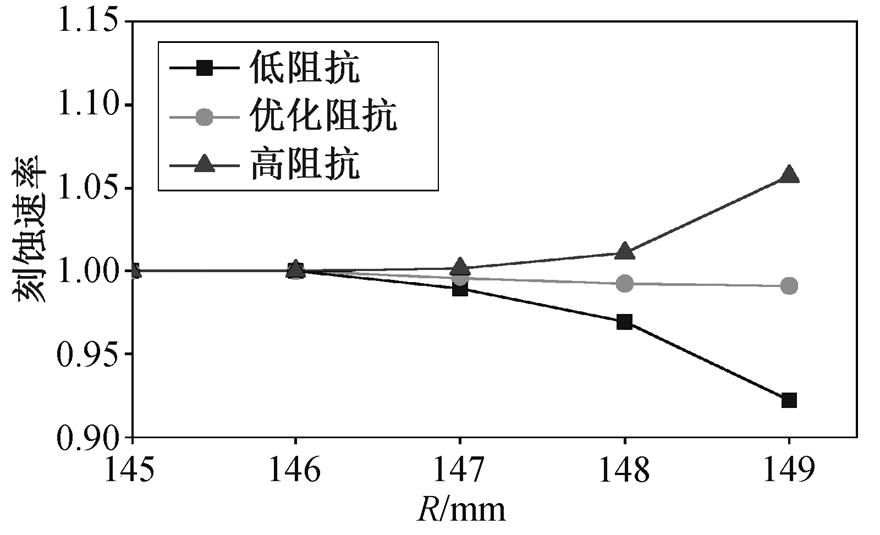

图 4 显示拟合后的刻蚀速率与不同阻抗(高、低和优化阻抗)的关系。随着半径的增大, 在低阻抗时刻蚀速率逐渐变低, 高阻抗时刻蚀速率逐渐升高。在优化的阻抗下, 边缘的刻蚀速率与晶圆内部的刻蚀速率相当。并且, 这种方法可以连续地控制阻抗变大或缩小, 离子运动方向可以被实时地优化为垂直于晶圆表面, 使边缘的刻蚀速率与晶圆内部的刻蚀速率相当, 提高了刻蚀的均匀性。

图4 拟合后的刻蚀速率与不同阻抗的关系

Fig. 4 Relation between etching rate (fitting) and different impedance

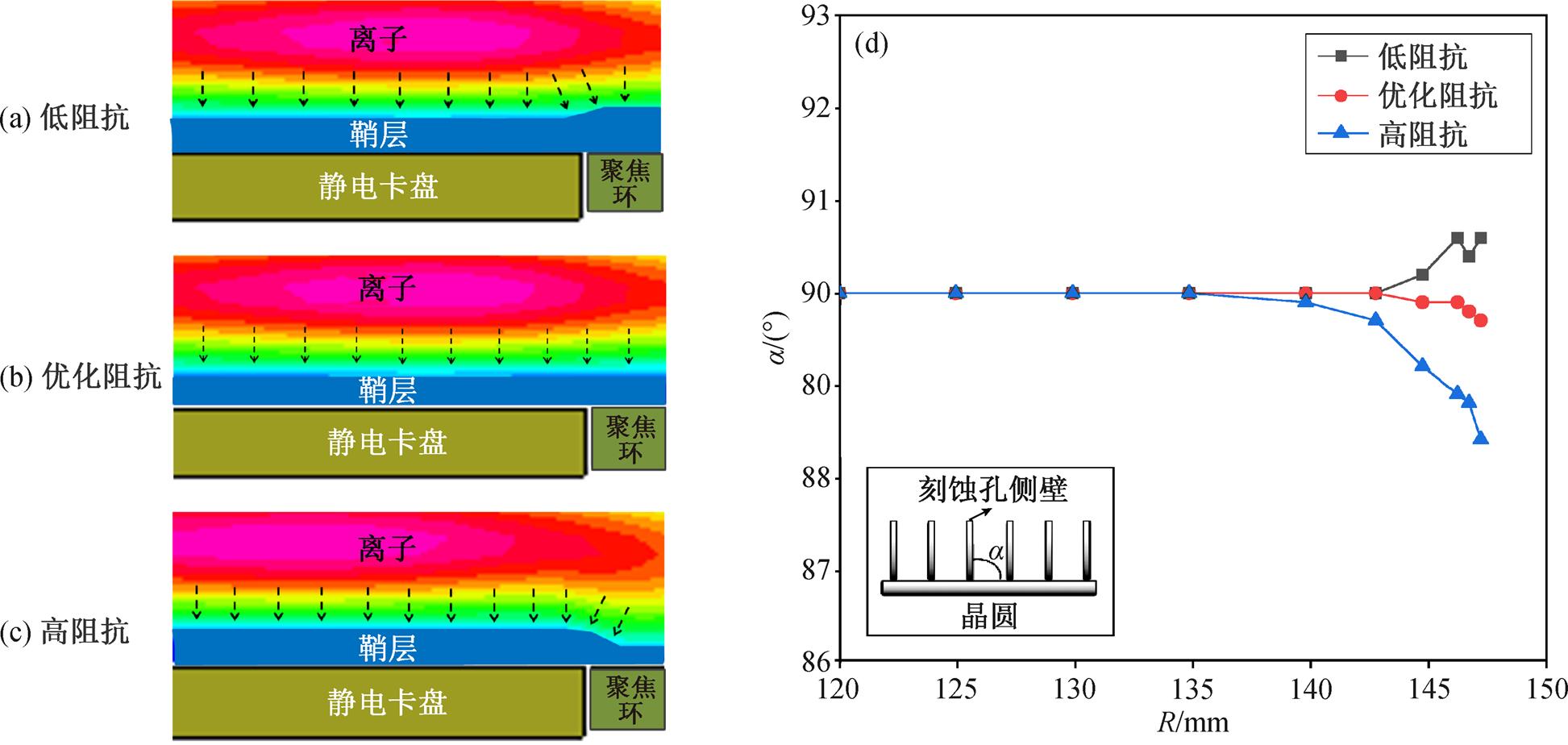

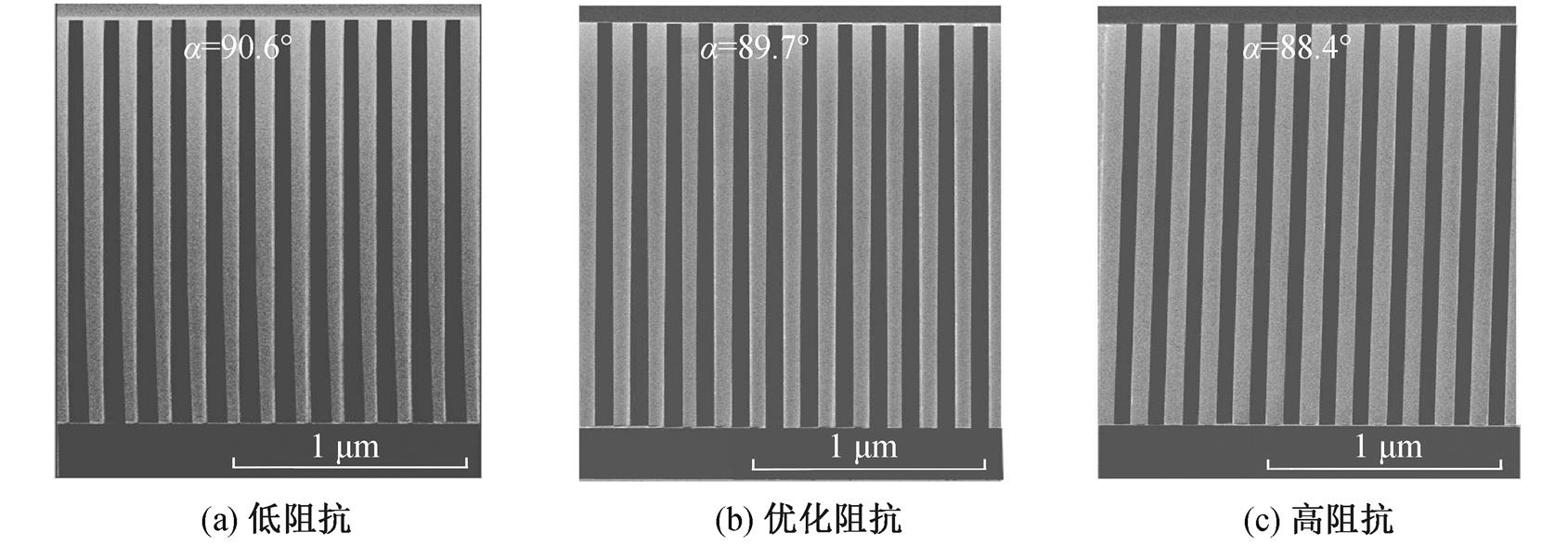

在 3D NAND ACL 的刻蚀工艺(深宽比约为 20)中, 测量在高、低和优化 3 种不同的阻抗下, 刻蚀形貌的倾斜角度, 结果如图 5 所示。倾斜角度的定义为刻蚀孔侧壁(side wall of holes)与晶圆在右侧的夹角 α, 如图 5(d)所示。倾斜角度从晶圆半径 R=140mm 的位置开始出现变化, 且随着半径增大, 在低阻抗时倾斜角度逐渐变大, 在高阻抗时倾斜角度逐渐变小, 在优化的阻抗下倾斜角度保持近似垂直的角度。图 6 为在半径 147.5mm 处, 高、低和优化 3种阻抗下刻蚀的晶圆的 SEM 截面图, 在优化的阻抗设定下, 可以明显减少边缘刻蚀出现的角度倾斜现象。

图5 刻蚀倾斜角与不同阻抗的关系

Fig. 5 Relation between etching profile angle and different impedance

可变电容的低阻抗设定会导致较高的射频功率耦合到聚焦环区域, 增加边缘区域等离子鞘层区的厚度, 离子运动方向发生如图 5(a)所示的向晶圆外侧倾斜。因此, 随着边缘阻抗的减少, 刻蚀形貌表现为向晶圆边缘倾斜(图 6(a)中低阻抗), 在半径为 147.5mm 处刻蚀倾角为 90.6°。同理, 可变电容的高阻抗设定会导致较低的射频功率耦合到聚焦环区域, 减小边缘区域等离子鞘层区的厚度, 离子运动方向发生如图 5(c)所示的向晶圆内侧倾斜。因此, 随着边缘阻抗的增加, 刻蚀形貌表现为向晶圆内侧倾斜(图 6(c)中高阻抗), 在半径为 147.5mm 处刻蚀倾角为 88.4°。当可变电容设置为优化阻抗时, 会将适量的射频功率耦合到聚焦环区域, 边缘等离子体鞘层轮廓未发生畸变, 获得垂直的刻蚀形貌(图6(b)中优化阻抗), 在半径为 147.5mm 处刻蚀倾角为 89.7°。

本文提出一种利用调整边缘阻抗的工艺优化方法, 可以连续实时地调整边缘离子的运动轨迹, 实现对边缘离子运动方向的控制。在此过程中, 离子的运动方向可以被优化为垂直于晶圆表面, 获得良好的刻蚀均匀性及垂直的刻蚀形貌。另外, 在等离子刻蚀中, 聚焦环会被不断地消耗, 边缘离子的运动轨迹也会出现逐渐倾斜。利用这种调整边缘阻抗的方法, 可以补偿由于聚焦环被消耗导致的等离子体边缘鞘层畸变, 保持边缘垂直的离子运动方向和刻蚀均匀性。

图6 在不同阻抗条件下刻蚀的晶圆SEM截面图(半径为147.5 mm处)

Fig. 6 SEM cross section after etching under different impedance (radius is 147.5 mm)

参考文献

[1]Moore G E. Progress in digital integrated electronics. International Electron Devices Meeting, 1975, 21: 11-13

[2]Paolo G, Taffy K, Linda W, et al. International technology roadmap for semiconductors 2.0. ITRS 2.0 publication [EB/OL]. (2015-07-11) [2018-09-06]. http://www.itrs2.net/itrs-reports.html

[3]Singh H. 克服 3D NAND 规模化生产面临的挑战. 中国集成电路, 2018(3): 54-56

[4]Rino M, Seiichi A, Luca C. Array architectures for 3-D NAND flash memories. Proceedings of the IEEE, 2017, 105(9): 1634-1649

[5]Babaeva N Y, Kushner M J. Ion energy and angular distributions into the wafer-focus ring gap in capa-citively coupled discharges. J Phys D: Appl Phys, 2008, 41(6):062004

[6]Denpoh K. Simulation of ion energy and angular distribution functions using Monte Carlo method coupled with multidimensional radio frequency sheath model developed utilizing COMSOL multiphysics. Japanese Journal of Applied Physics, 2014, 53(8):080304

[7]Vincent M D, Avinoam K. Plasma etching yesterday, today, and tomorrow. Journal of Vacuum Science & Technology A, 2013, 31(5): 050825

[8]Ishikawa K, Karahashi K, Ichiki T, et al. Progress and prospects in nanoscale dry processes: how can we control atomic layer reactions?. Japanese Journal of Applied Physics, 2017, 56:06HA02

[9]Jon M, Yuhou W, Damon T G, et al. Detection sys-tem for tunable/replaceable edge coupling ring: US, 20170263478 [P/OL]. (2017-09-14) [2018-09-06]. https://worldwide.espacenet.com/publicationDet-ails/ originalDocument? CC=US&NR=2017263478& KC =&FT=E#

Active Ion-Trajectory Control at the Wafer Extreme Edge in Plasma Etch

Abstract As the impedance of the conventional plasma etching system at the edge of the wafer is not consistent with that at the center of the wafer, the movement trajectory of ions at the edge of the wafer is deviated and it is difficult to meet the more stringent requirements on etching process uniformity and high aspect ratio. A method to optimize the movement direction of edge ions by adjusting the impedance of the wafer edge is proposed which can continuously and real-time adjust the movement trajectory of edge ions and control the direction of edge ions. The results show that the direction of ion movement can be optimized to be perpendicular to the surface of the wafer, the uniformity of the edge etch rate is optimized, and the vertical etching morphology is obtained.

Key words plasma etching; 3D NAND; ion movement trajectory; edge impedance; etching uniformity

doi: 10.13209/j.0479-8023.2019.066

修回日期: 2019-01-01

收稿日期: 2018-09-17;