图1 提出的异步低功耗RSA结构

Fig. 1 Proposed asynchronous low power RSA structure

张奇惠 曹健 曹喜信 于敦山 张兴†

北京大学软件与微电子学院, 北京 102600; †通信作者, E-mail: zhx@pku.edu.cn

摘要提出一种适用于智能卡和电子标签的异步低功耗 RSA 电路结构及其模乘电路结构, 使用GTECH的优化方法和BrzCallMux的实现策略, 基于TSMC130nmCMOS标准工艺进行 ASIC 实现。结果表明, 所提出的异步低功耗RSA的面积最低仅为其他RSA面积的4%, 一次加解密时间最低仅为其他RSA加解密时间的0.216%, 功耗最低仅为其他RSA功耗的16.99%。

关键词异步; 低功耗; RSA; GTECH; ASIC

随着片上网络(NoC)和片上系统(SoC)复杂度和功耗的不断增加, 同步电路设计中的时钟偏移、功耗、多时钟域集成和可复用问题等愈发凸显。

异步电路具有低功耗、高平均性能、剔除了全局时钟树、对环境和工艺的高度自适应、更少的电磁辐射噪声、更好的模块化和兼容性等优势[1–3], 并且因其对环境变化的自适应性及对数据流控制的固有机制, 在很多场合的效果显著优于同步电路。

RSA 算法是一种非对称加密算法, 在密码学领域具有划时代的意义。RSA 加密算法的基本原理是数论原理中的大数分解问题, 是当前应用最广的非对称加密算法, 可以用于加密和数字签名。RSA加密算法的安全性极高, 可以抵抗当前所有的已知攻击方法, 被国际标准化组织推荐为公钥数据加密标准。

目前, 智能卡和电子标签领域发展迅速, 对于安全性能、成本和功耗的需求也不断增加。目前, 已经提出很多同步 RSA 电路结构和安全策略[4–8]。基于请求–应答的握手机制和基于锁存器的存储结构, 使得异步电路技术不仅可以提高安全芯片的抗攻击性能, 还可以有效地降低面积和功耗。因此, 开展异步低功耗 RSA 电路的设计和实现研究极具理论和现实意义。

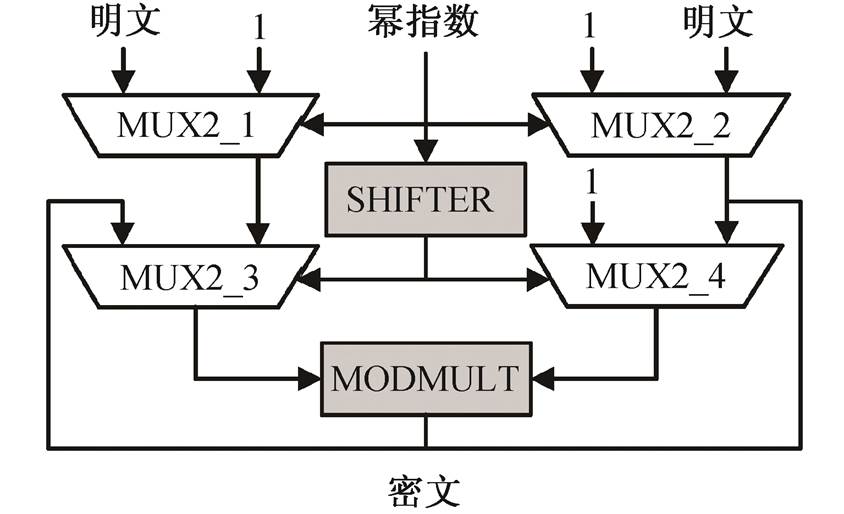

图1 提出的异步低功耗RSA结构

Fig. 1 Proposed asynchronous low power RSA structure

本文提出的异步低功耗 RSA 结构包括 1 个移位器、1 个模乘器和 4 个选择器, 如图 1 所示。加密电路上电后, 首先锁存明文、幂指数和模; 然后根据幂指数的最低位, 使用MUX2_1和MUX2_2选择用于模乘运算的被乘数为明文或为 1, 并进行模乘运算; 将被乘数和乘数都选择为明文, 进行模幂运算; 使用移位器 SHIFTER 将幂指数右移一位; 根据幂指数右移后的最低位, 使用MUX2_3和MUX2_4 选择用于模乘运算的乘数为模幂输出或为1, 并进行模乘运算; 将被乘数和乘数都选择为模幂输出, 进行模幂运算; 重复以上步骤, 直到移位后的幂指数为0。

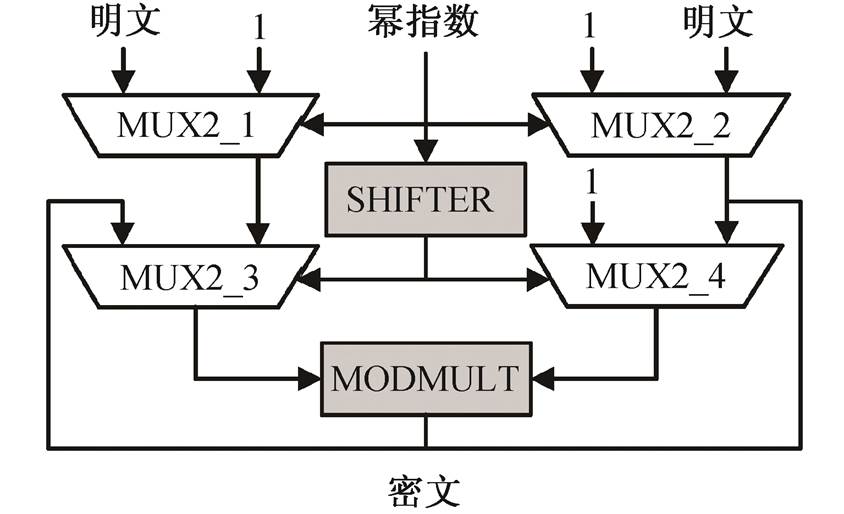

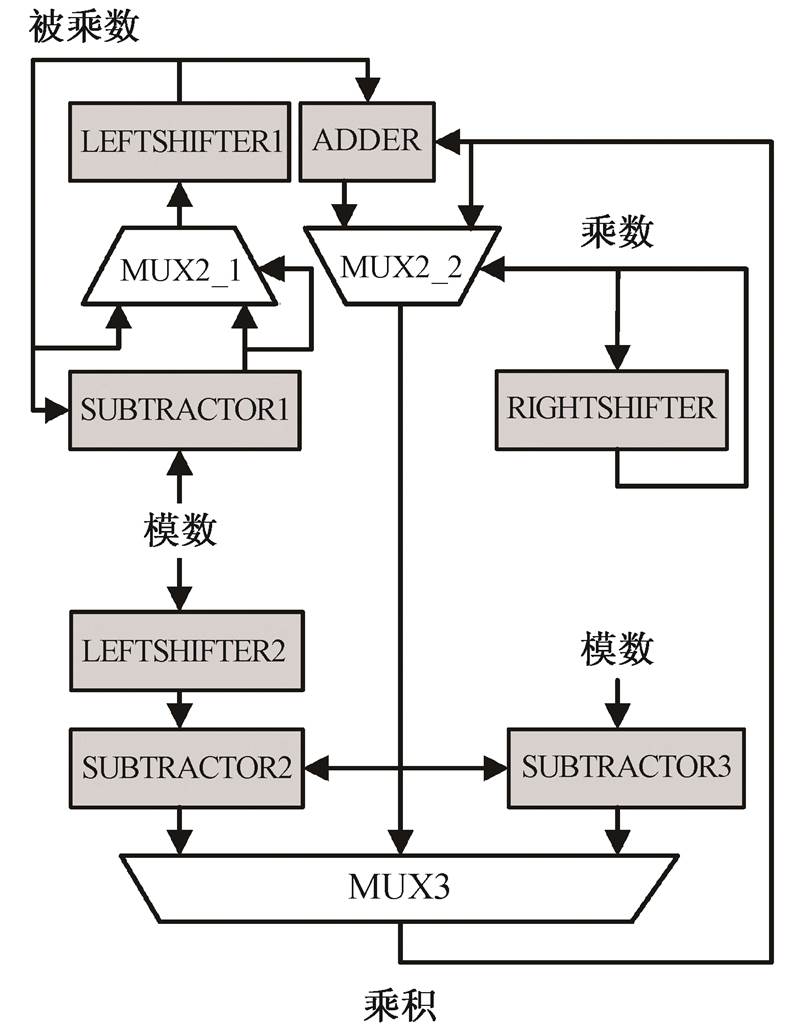

本文提出的异步低功耗 RSA 模乘结构包括 1个加法器、3 个减法器、3 个移位器和 3 个选择器, 如图 2 所示。首先使用移位器 LEFTSHIFTER2 将模左移一位; 然后使用加法器 ADDER 将乘积与被乘数相加, 根据乘数的最低位, 乘积 1 由加法器ADDER 的输出或者乘积通过 MUX2_2 选择得到; 乘积 2 由乘积 1 与模通过减法器 SUBTRACTOR3相减得到; 乘积 3 由乘积 1 与模左移一位通过减法器 SUBTRACTOR2 相减得到; 根据乘积 2 的最高位和乘积 3 的最高位, 通过 MUX3 选择得到乘积; 被乘数 1 由被乘数与模通过减法器 SUBTRACTOR1相减得到; 相减结果的次高位控制 MUX2_1 选择被乘数 1 是锁存相减后的结果, 还是锁存被乘数; 将被乘数 1 通过移位器 LEFTSHIFTER1 左移一位得到新的被乘数, 将乘数通过移位器 RIGHTSHIF-TER 右移一位得到新的乘数; 重复以上步骤, 直到移位后的乘数为0。

以上电路采用基于请求–应答的异步握手机制实现, 其基于锁存器的存储结构能够降低电路的面积, 其事件驱动的特性可以达到“极致”精细门控的效果, 能够显著地降低电路的动态功耗。

图2 提出的异步低功耗RSA模乘结构

Fig. 2 Proposed asynchronous low power RSA modular multiplication structure

异步电路的设计方法主要分为 3 类: 基于Petri网的异步设计、基于 VerilogHDL/VHDL 硬件描述语言的异步设计和基于行为级综合的异步设计。由于需要采用繁琐的网表输入, 所以基于 Petri 网的异步设计只适用于小规模电路。由于需要自定义控制电路以及详细分析电路时序, 所以基于 VerilogHDL/ VHDL 硬件描述语言的异步设计需要大量的人工参与, 效率偏低, 不利于工程实现。基于行为级综合的异步设计方法无需过多关注细节, 而将主要精力放在设计本身。本文采用面向语法的行为级综合异步设计方法, 结合异步 Balsa 综合工具[9]以及同步EDA工具, 适合大规模异步集成电路的设计和实现。

在 Balsa 推荐的异步电路设计和实现流程中, 异步单元库由同步单元库中的基本单元构建得到, 经过 Balsa 综合后, 直接得到基于同步基本单元库的门级网表。

采用基于 GTECH 的优化方案, 可有效地降低异步设计的面积和功耗。使用 GTECH 公用单元库构建异步单元库, 然后将由 Balsa 综合后生成的基于 GTECH 的门级网表导入 Design Compiler 中进行综合, 并映射到目标单元库, 生成基于目标单元库的门级网表。结果表明, 未使用 GTECH 优化方案前, C 单元由 AO222 (34μm2)实现, 使用GTECH 优化方案后, C单元由面积较小的MAJ3 (14μm2)实现, 面积降低至原来的43%。

异步 BrzCallMux 单元的实现包括多输入和二输入两种情况。原始的多输入 BrzCallMux 由“OR+ C+NKEEP+TRINV”实现, 而有些同步基本单元库中没有实现 NKEEP 和 TRINV 所需要的busholder和 tri-state 门。二输入BrzCallMux由“SRFF+AND +MUX2”实现, 如果不先对 SRFF 的输出赋初值, 则无法正确仿真, 并且下载到 FPGA 开发板上功能也将不正确。针对以上两个问题, 本文采用“OR+ C+NAND”的实现策略。实验结果如表 1 所示, 二输入 BrzCallMux_48_2 的面积从1007.6 μm2增加到1367.6 μm2, 而多输入 BrzCallMux_48_8 的面积从12124.1μm2大幅度地降低为6311.2 μm2, 降幅高达 48%。从表 1 可以看出, 与原始实现策略相比, 使用“OR+C+NAND”实现的二输入 BrzCallM-ux 的面积稍有增加, 但多输入 BrzCallMux 的面积大幅度降低。

表1 BrzCallMux单元实现前后的面积比较

Table 1 Area comparison of pre and post substitute of BrzCallMux components

BrzCallMux单元实现策略面积/μm2 BrzCallMux_48_2SRFF+AND+MUX21007.6 OR+C+NAND1367.6 BrzCallMux_48_8OR+C+NKEEP+TINV12124.1 OR+C+NAND6311.2

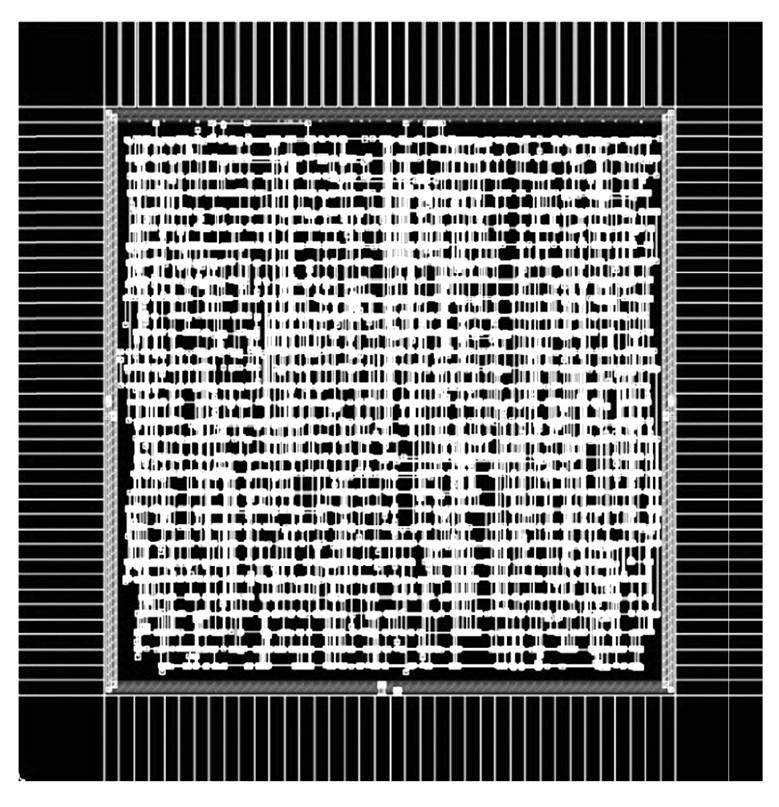

基于 TSMC 130nm CMOS 标准工艺, 本文提出的异步低功耗 RSA 芯片分别使用 Balsa, Design Compiler, IC Compiler, StarRC和PrimeTime进行设计、综合、布局布线、参数提取以及功耗评估, 芯片版图如图3所示。

图3 异步低功耗RSA安全芯片的版图

Fig. 3 Layout of proposed asynchronous low power RAS security chip

基于 32-bit 位宽, 将本文提出的异步 RSA 分别与其他异步和同步 RSA 进行对比, 结果如表 2所示。

与在 OpenCores 上采用相同工艺实现的同步RSA 相比, 本文提出的异步低功耗 RSA 的面积是其面积的 90.2%。与采用 STM65nm CMOS 工艺实现的异步 RSA 相比, 本文异步低功耗 RSA 的门数分别仅是其门数的 4%和 5.8%。当前异步低功耗RSA 结构中的异步基本单元(如 C 单元、S 单元和 T单元等)均由同步基本单元搭建, 如果定制这些异步基本单元, 面积还可以再减少30%[12]。

自动布局布线之后, 将导出的 DEF 文件使用StarRC 进行参数提取, 并生成 SPEF 文件, 然后使用 PrimeTime 转化为 SDF 文件, 并反标到版图后的门级网表中进行时序仿真, 结果如表 2 所示。由表 2 可知, 执行一次 RSA 加解密所需时间分别为34.084, 104.31, 0.240和0.225 μs, 提出的异步低功耗 RSA 的一次加解密时间最少仅为其他 RSA 加解密时间的0.216%。

表2 异步低功耗RSA与其他同步/异步RSA的比较

Table 2 Comparison between proposed asynchronous low power RSA and other synchronous/asynchronous RSA implementations

RSA设计工艺/nm面积/门数时间/μs功耗/mW 内部开关泄露总计 异步RSA[10]STM 6513227434.0842.6254.8342.2019.66 异步RSA[11]STM 6591276104.3104.3611.3422.1627.86 同步RSATSMC 13058750.24027.1012.0700.02929.20 本文的异步RSATSMC 13053000.2253.9221.0330.0074.96

采用 6 组不同位长的明文进行加解密操作, 结果如表 2 所示。由表 2 可以看出, 除 Internal 功耗外, 本文提出的异步 RSA 的其他各项功耗和总功耗都是最低的, 总功耗最低值仅为其他 RSA 总功耗的16.99%。

在OpenCores上, 同步 RSA 实现的功耗主要消耗在Internal的功耗上(占总功耗的 92.81%), 而Switching功耗仅占总功耗的7.09%。本文提出的异步RSA的Switching功耗却占总功耗的 20.83%。这是由于异步电路具有较小的存储单元, 因而控制逻辑和握手电路较复杂, 导致 Switching 功耗所占比重较大。

本文提出一种异步低功耗 RSA 电路结构及其模乘电路结构, 并进行 ASIC 实现。采用基于请求–应答的异步握手机制进行设计,能够达到精细门控的目的,使得没有参与握手的电路只消耗静态功耗,因此降低了 RSA 电路的功耗。实验结果表明, 本文提出的异步低功耗 RSA 芯片的面积最小仅为其他 RSA 面积的 4%, 一次加解密时间最少仅为其他 RSA 加解密时间的 0.216%, 其功耗最低仅是其他 RSA 功耗的 16.99%。如果定制异步基本单元, 本文提出的异步低功耗 RSA 芯片的面积和功耗还可以大幅度地降低。另外, 本文提出的异步低功耗RSA 电路结构非常适合应用于集成到智能卡和电子标签中。

参考文献

[1]Spars J, Furber S. Principles of asynchronous cir-cuit design — a systems perspective. Boston: Kluwer, 2001: 3–4

J, Furber S. Principles of asynchronous cir-cuit design — a systems perspective. Boston: Kluwer, 2001: 3–4

[2]Ebergen J, Finchelstein D,Kao R, et al. An evalua-tion of asynchronous stacks. IEEE Design & Test of Computers, 2011, 28(5): 52–61

[3]Zhang Q H, Cao J, Cao X X, et al. An asynchronous design method and its application on a low-power RFID baseband processor // IEEE Advanced Informa-tion Technology, Electronic and Automation Control Conference. Chongqing, 2017: 328–331

[4]Zhao B, Wang L H, Jiang K, et al. An improved power attack on small RSA public exponent // IEEE Inter-national Conference on Computational Intelligence and Security. Wuxi, 2016: 578–581

[5]Huang X M, Wang W. A novel and efficient design for an RSA cryptosystem with a very large key size. IEEE Transactions onCircuits and SystemsII: Express Briefs, 2015, 62(10): 972–976

[6]Bhadada R, Sharma A. Montgomery implantation of ECC over RSA on FPGA for public key cryptography application // IEEE International Conference on Emerging Technology Trends in Electronics, Commu-nication and Networking. Surat, 2014: 1–5

[7]Shao C, Li H Y, Zhang X L. Cryptographic implemen-tation of RSA for ion fault injection attack // IEEE Consumer Communications and Networking Confe-rence. Las Vegas, 2014: 791–796

[8]Borodzhieva A N. Software implementation of a mo-dule for encryption and decryption using the RSA algorithm // IEEE International Scientific Conference Electronics. Sozopol, 2016: 1–4

[9]Moreira M T, Magalhães F G, Gibiluka M, et al. BaBaNoC: an asynchronous network-on-chip des- cribed in Balsa. IEEE International Symposium on Rapid System Prototyping, 2013, 46(1): 37–43

[10]Matheus M, Bruno O, Julian P, et al. A 65 nm stan-dard cell set and flow dedicated to automated asyn-chronous circuits design. IEEE International SOC Conference, 2011, 42(4): 99–104

[11]Matheus M, Bruno O, Fernando M, et al. Impact of C-elements in asynchronous circuits // IEEE Interna-tional Symposium on Quality Electronic Design. Santa Clara, 2012: 437–343

[12]Teifel J. Asynchronous cryptographic hardware de- sign. IEEE International Carnahan Conference on Secu-rity Technology, 2006, 23(10): 221–227

Design and Implementation of an Asynchronous Low Power RSA Circuit Structure

ZHANG Qihui, CAO Jian, CAO Xixin, YU Dunshan, ZHANG Xing†

School of Software and Microelectronics, Peking University, Beijing 102600; † Corresponding author, E-mail: zhx@pku.edu.cn

AbstractAn asynchronous low power RSA circuit structure and its modular multiplication circuit structure for smart cards and RFID tags are proposed. By using GTECH optimization scheme and BrzCallMux implementation strategy, ASIC implementation is carried out based on a TSMC 130 nm standard CMOS technology. Experimental results show that the area of the proposed asynchronous low power RSA is only 4% of that of another asynchro-nous RSA, its average time to perform a cryptographic operation is only 0.216% of that of another asynchronous RSA, and its power consumption is only 16.99% of that of its corresponding synchronous counterpart.

Key wordsasynchronous; low energy; RSA; GTECH; ASIC

中图分类号TN492

doi:10.13209/j.0479-8023.2018.046

收稿日期:2017–09–10;

修回日期:2017–10–17;

网络出版日期:2018–10–22