图1 采用混合电容切换模式的5-bit SAR ADC工作原理

Fig. 1 5-bit SAR ADC with mixed-monotonic capacitor switching scheme

葛彬杰 李琰† 俞航 冯晓星

深圳大学计算机与软件学院, 深圳 518060; † 通信作者, E-mail: liyan@szu.edu.cn

摘要 提出一种应用于逐次逼近型模数转换器的混合电容切换模式。该模式包含两个幅度相同但单调性相反的开关电容阵列, 无需任何额外的稳压电源和电容补偿阵列, 通过差分电压自身的互相补偿, 实现共模电压的稳定。利用上述技术, 基于 0.18μm 的 CMOS 工艺实现一个转换速率为 50MS/s, 分辨率为 10-bit 的 SAR ADC。设计过程中采用开窗逻辑, 减小了比较器输出信号到DAC控制信号的传输时间; 采用包含自适应延时逻辑的比较环路, 缩短了 SAR ADC 低位比特的转换时间。测试结果表明, 所设计的 SAR ADC在50 MS/s的转换速率下, 可以实现57.31 dB的SNDR, 1.81 LSB的INL以及0.98 LSB的DNL。

关键词 混合电容切换; 共模稳定; SAR ADC

逐次逼近型(successive approximation register, SAR)模数转换器(analog-to-digital converter, ADC)结构简单, 无需高性能的模拟放大电路, 仅需要一个比较器, 因此具有极低的静态功耗。SAR ADC 的转换速度取决于其内部 DAC 的稳定速度、比较器的再生速度和数字逻辑的延迟时间; 精度取决于DAC 电容的匹配精度。因此, 该类型 ADC 显著地受惠于集成电路制造工艺的进步。基于上述优点, 该类 ADC 的研究越来越受到关注, 已取得显著的成果。全异步控制逻辑的发明使得 SAR ADC 在转换过程中无需“过采样”时钟, 从而摆脱了对高速时钟的依赖, 进一步降低了 ADC 系统的整体功耗。电容校正算法的发展使得 ADC 摆脱了对高精度模拟器件的依赖, 利用数字工艺下的 MOM 电容即可实现高转换精度。因此, SAR ADC可以在纯数字工艺上实现高速度、高精度的模数转换, 且具有极大的功耗优势, 因此SAR ADC最适合与数字电路进行 SOC集成。

当前, 有关SAR ADC的研究主要有两个方向: 1)研究系统级的创新, 通过时间交织的方式进一步提高 ADC 的转换速度[1], 或者通过 SAR ADC 与流水线 ADC[2-3]或者过采样 ADC[4]的结合实现转换 精度的提升; 2)通过对 SAR ADC 内部 DAC 电容切换方式的重新分配, 实现动态功耗的进一步降低[4–7]。

电荷重分配型SAR ADC是通过设计合理的开关电容阵列, 将模拟输入信号逐步转换成数字代码, 与电阻分压型 SAR ADC 相比, 具有功耗低和匹配好的优点, 是目前主流的实现方式。Liu 等[4]提出一种新颖的单调电容切换方式, 与基于传统电容切换方式实现的 SAR ADC 相比, 动态功耗可以减小81%, 电容面积可以减小一半。但是, 该结构的SAR ADC 在转换过程中, 其比较器输入的共模电压(common-mode voltage, Vcm)会一直朝 GND 或者VDD 单调变化, 导致比较器的转换增益随着信号而变化, 给 ADC 引入与信号相关的失调电压, 恶化 ADC 的线性度和噪声性能[4,6]。为了稳定比较器输入的共模电压, 文献[5–11]引入一个额外的直流电压源, 该直流电压源需要较大的驱动能力, 因此需要较大面积的稳压电容; 文献[12]引入额外的电荷补偿阵列, 该阵列会改变原有 DAC 的电容比例, 同时需要额外的开关控制信号, 使得 SAR 的控制逻辑更复杂。

本文提出一种应用于逐次逼近型模数转换器的混合电容切换逻辑, 通过将传统的单调切换逻辑拆分成两个单调相反的开关电容阵列, 使得比较器输入的共模电压在两个方向的相反变化互相抵消, 无需引入任何额外的电路结构, 即可实现共模电压的稳定。

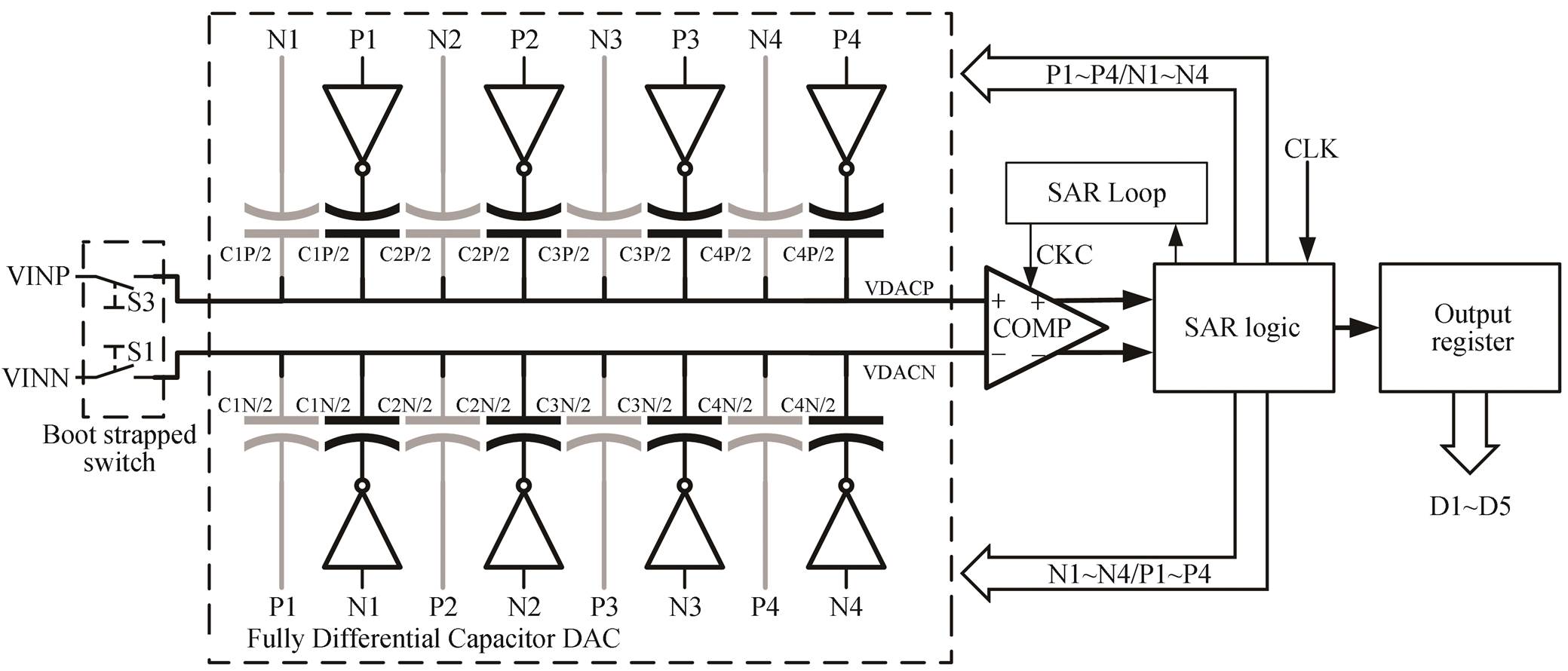

图 1 是一个采用本文混合电容切换模式的 5-bit SAR ADC, ADC 的参考电压等于电源电压。在每 个转换步骤, DAC 电容阵列的输出电压朝两个相反的方向变化, 并逐步靠近 VDD/2, 完成模拟电压的数字转换。图 1 中单调递减的电容切换阵列用黑色电路表示, 单调递增的电容切换阵列用灰色电路表示, 灰色和黑色的电容切换阵列的电容大小完全相同。从图 1 可知, 混合电容切换阵列不需要额外的参考电压对共模电压进行稳定。

混合电容切换阵列的工作原理描述如下。在ADC的采样相位, 所有的正向开关Pi (i=1~4)和负向开关 Ni (i=1~4)都复位到地电位, 同时输入的模拟信号储存在电容的上极板。在 ADC 的转换相位, 比较器对电容型 DAC 的差分输出电压 VDACP 和VDACN 进行比较, 并得到对应bit的比较结果, 即Pi 和 Ni; 同时 Pi 和 Ni 反馈至电容型 DAC 后, 会使 DAC 在下一次比较开始之前, 根据前一个周期的比较结果更新其输出电压, 供比较器进行下一个bit的比较, 如此循环, 完成整个 SAR ADC 的模数转换。

图1 采用混合电容切换模式的5-bit SAR ADC工作原理

Fig. 1 5-bit SAR ADC with mixed-monotonic capacitor switching scheme

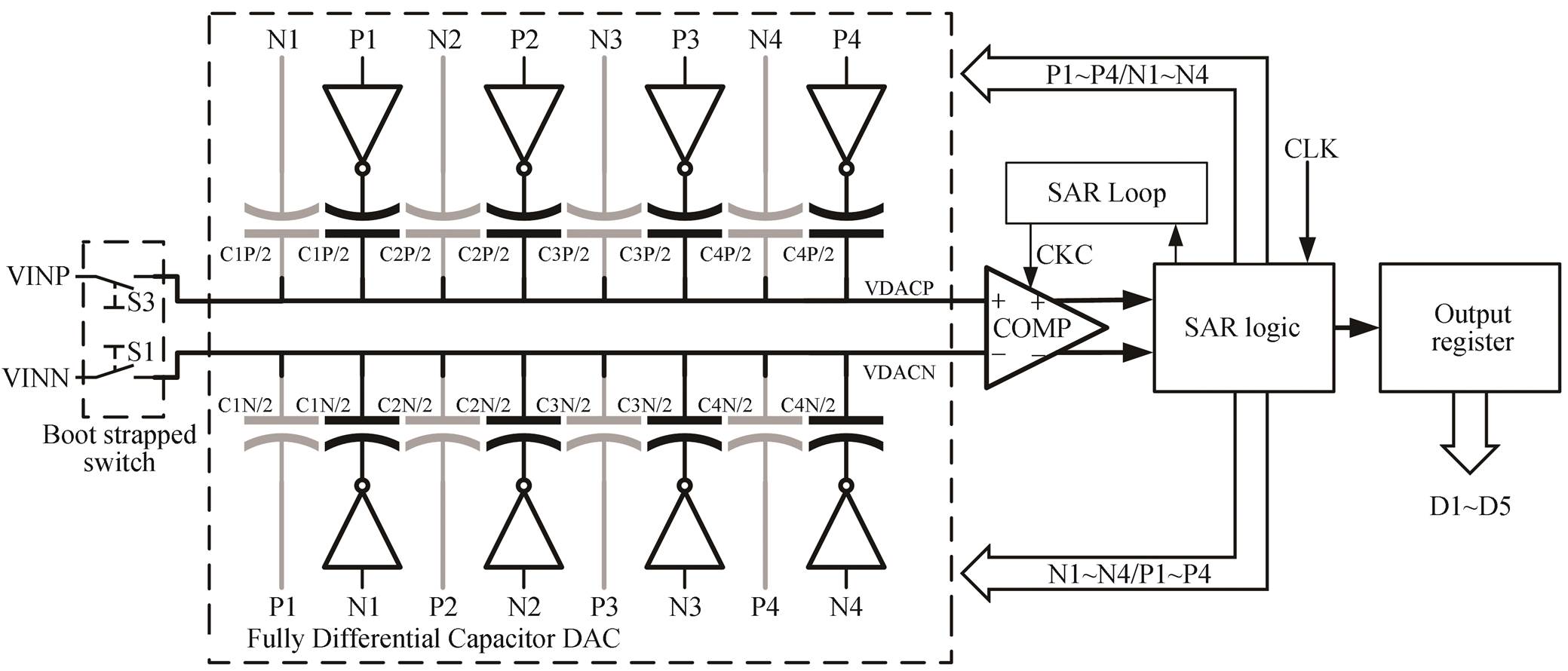

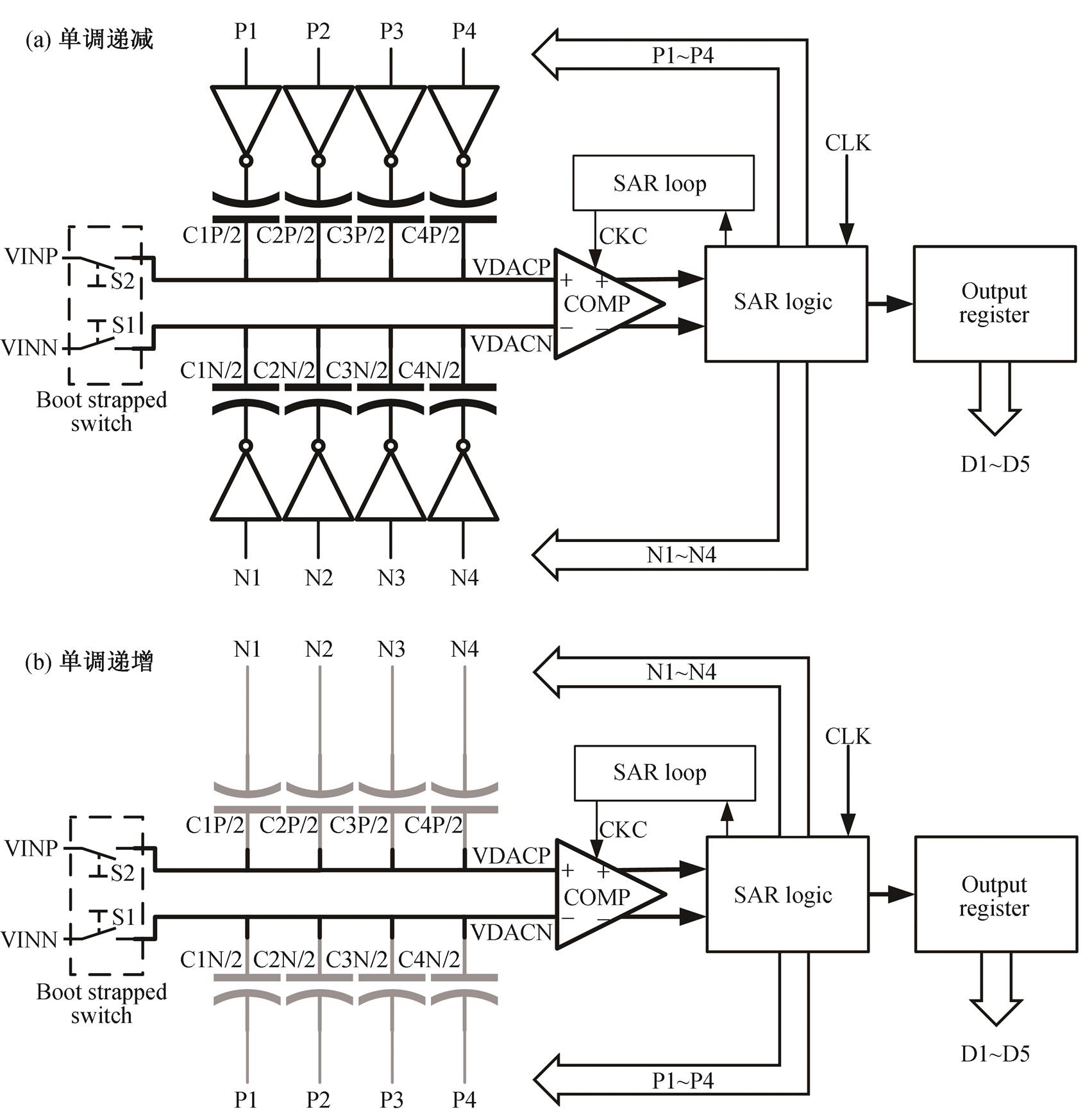

为了更好地理解本文提出的混合电容切换模式, 图 1 中的 SAR ADC 被拆分成单调递减和单调递增的 ADC, 原理如图 2 所示。对如图 2(a)所示的单调递减的 SAR ADC 而言, 如果 VDACP 大于VDACN, 那么正向的开关信号 Pi 被置到电源电压, 负向开关信号 Ni 则维持不变。此时电容 CiP/2 的下极板接到地点位, 同时 VDACP 的电压会降低。SAR ADC 转换的过程就是将 DAC 输出电压较高的一边拉低的过程, DAC 输出电压的变化见图 3(a)。与此相反, 图 2(b)所示的单调递增 SAR ADC 中, 其 VDACP 支路的电容由负向开关信号 Ni 控制, 而 VDACN 支路的电容由正向开关信号 Pi 控制。因此电容 CiN/2 的下极板电压会接到电源电压, 同时 VDACN 的电压会升高, 整个 SAR ADC 进行模数转化的过程在 DAC 的输出上体现为将差分输出电压较低的一端电压抬高的过程, DAC 电压的变化见图 3(b)。单调递增和单调递减的两个 ADC 的电容阵列完全相同, 因此 DAC 产生的相反变化正好互相抵消, 由此实现比较器输入共模电压的稳定。完整混合电容切换模式实现的 SAR ADC 的 DAC 输出电压变化如图3(c)所示。

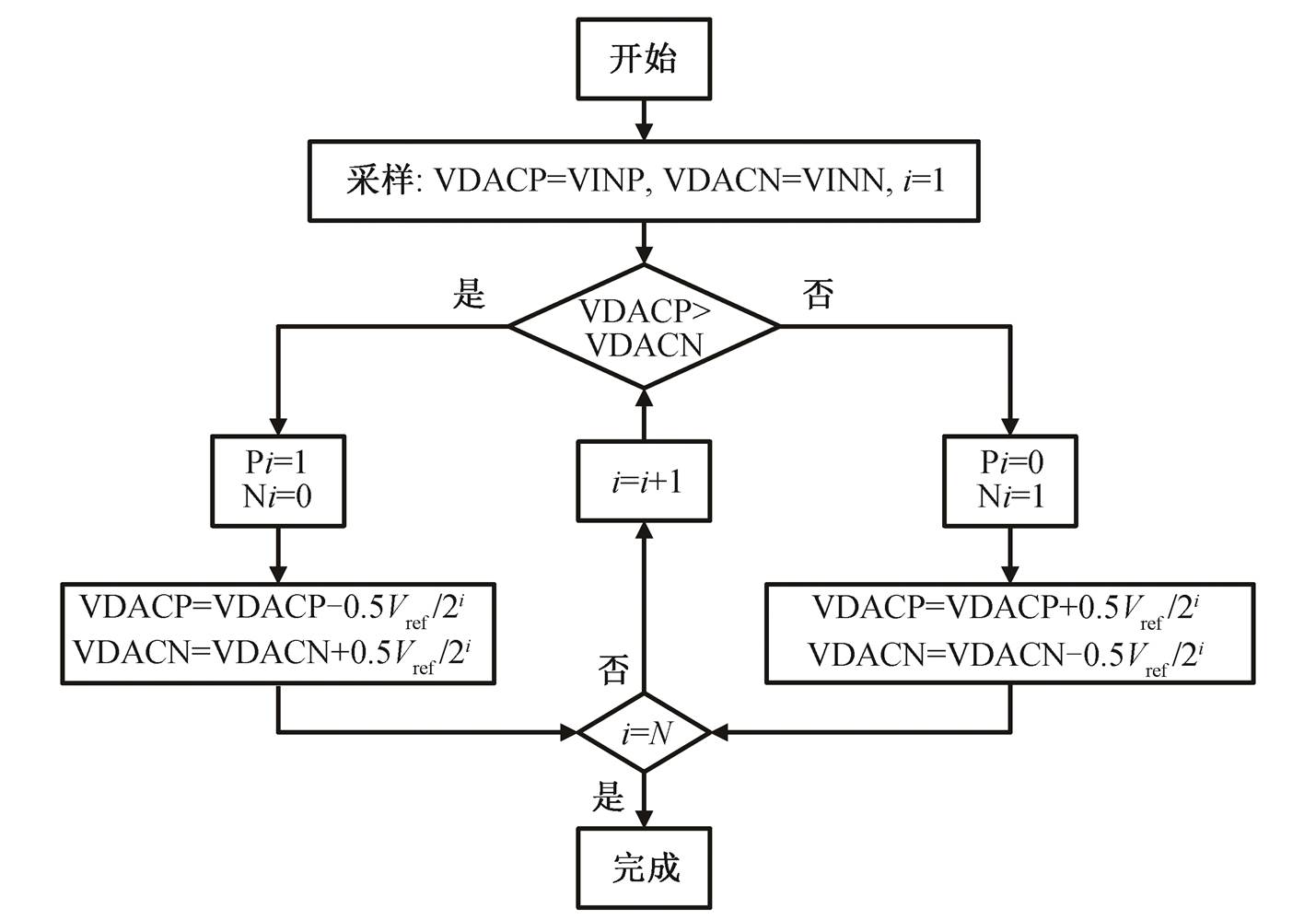

上述 SAR ADC 的工作流程如图 4 所示, ADC的采样完成之后, 可以直接进行比较, 因此可以减少一半的电容面积。

图2 拆分后的单调SAR ADC

Fig. 2 Split monotonic SAR ADCs

图3 SAR ADC比较器输入电压的变化

Fig. 3 SAR ADC comparator input settling

图4 SAR ADC工作流程

Fig. 4 Flow chart of SAR ADC

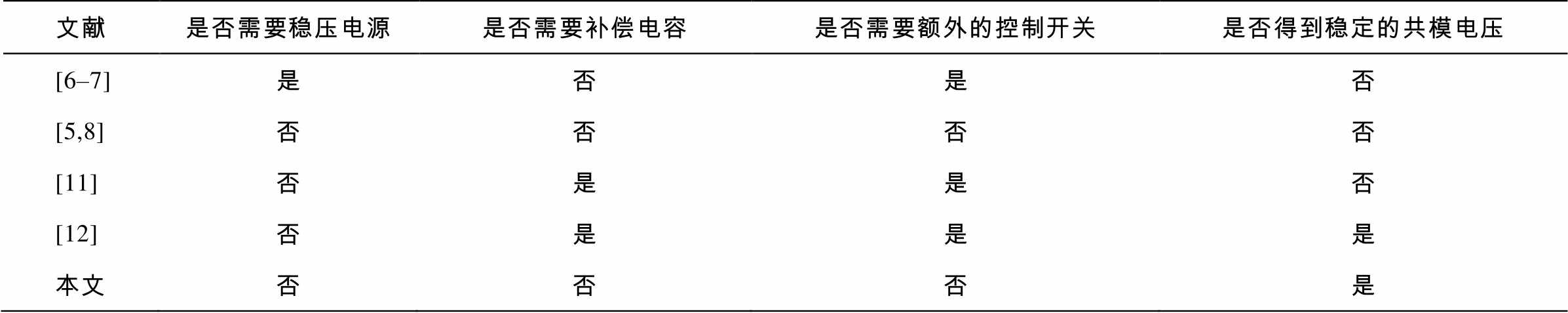

本文提出的混合电容切换方式与其他文献实现方式的对比见表 1。可以看出, 本文提出的新颖的电容切换方式无需任何额外的电容补偿阵列和稳压电源, 因此芯片的功耗和面积都是最优的。

为了进一步验证本文提出的混合电容切换模式, 基于 0.18 μm 的 CMOS 工艺, 设计一个转换速率为 50 MHz, 分辨率为 10 Bit 的全异步 SAR ADC。如图 5 所示, ADC 的电容阵列采用两段式结构, 以便减小电容的面积。图 5 中的 DAC 仅最高位4 个Bit 控制的电容采用混合的切换模式, 余下的 5个则采用传统的单调递减的切换模式。上述设计基于以下两点考虑: 1) DAC 高位电容引起的共模电压变化占主导地位, 因此低位电容阵列共模电压下降产生的影响可以忽略; 2) DAC 低位的电容值较小, 即使在用串联方式进行拆分的情况下, 由于版图空间较小, 会导致布线比较复杂。

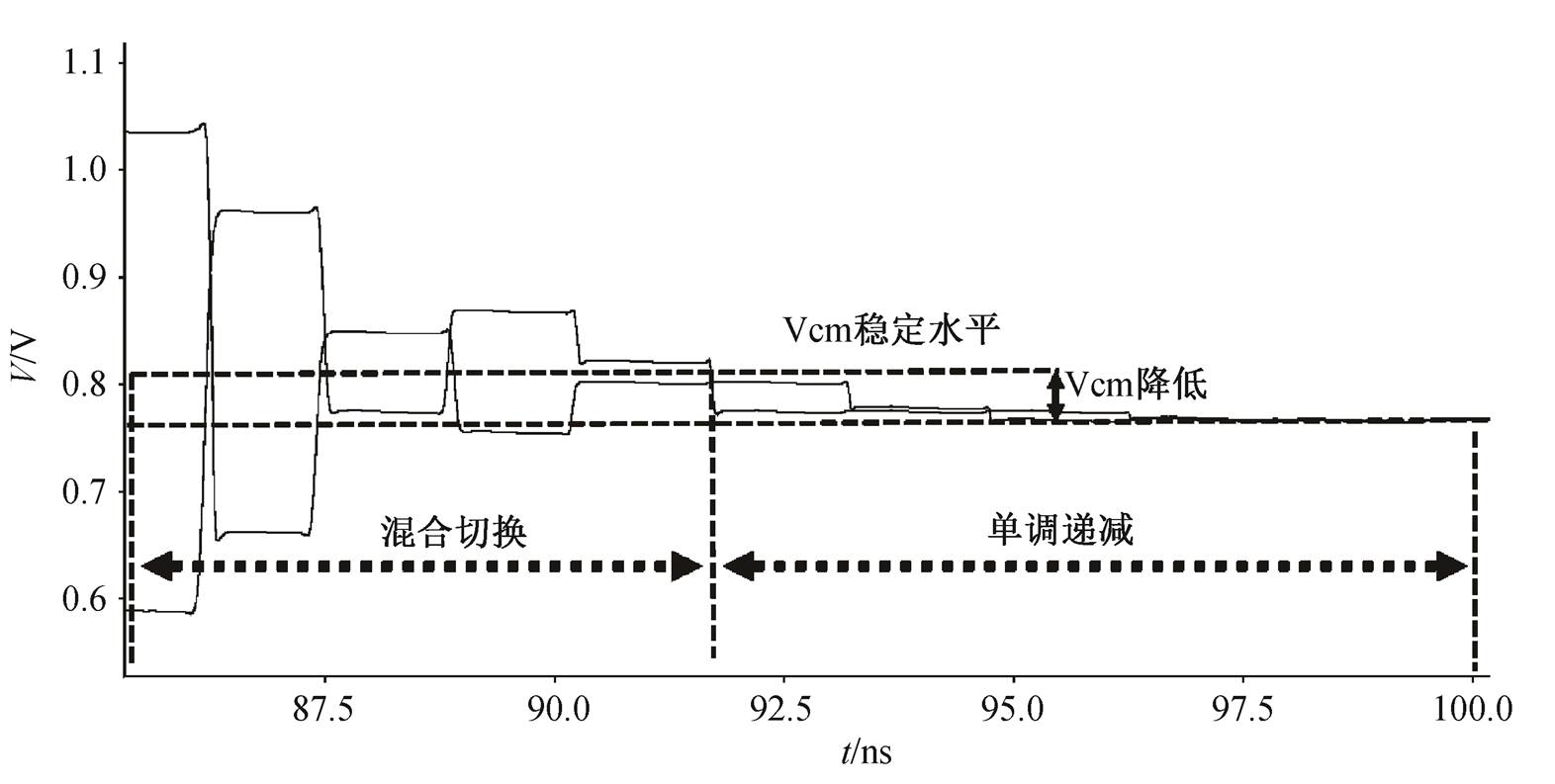

对图5的 SAR ADC 进行瞬态仿真, 比较器输入共模电压的变化见图 6。仿真结果显示, 在 SAR ADC 处于高位转换(最高位的 4 个 Bit)时, 电容阵列进行混合切换, 因此比较器的输入共模电压维持不变; 在SAR ADC处于低位转换(其余 5 个Bit)时, 电容阵列进行单调递减的切换模式, 比较器的共模输入电压逐渐降低, 但在完成所有 Bit 的比较时, 共模电压的降低幅度小于 0.3 V, 与预想的情况一致。

表1 不同电容切换方式的比较

Table 1 Comparison of different switch scheme

图5 10位混合电容切换模式的SAR ADC

Fig. 5 Prototype of 10-bit proposed mixed-monotonic SAR ADC

图6 SAR ADC的比较器输入电压瞬态仿真波形

Fig. 6 Comparator input transient waveform of prototype SAR ADC

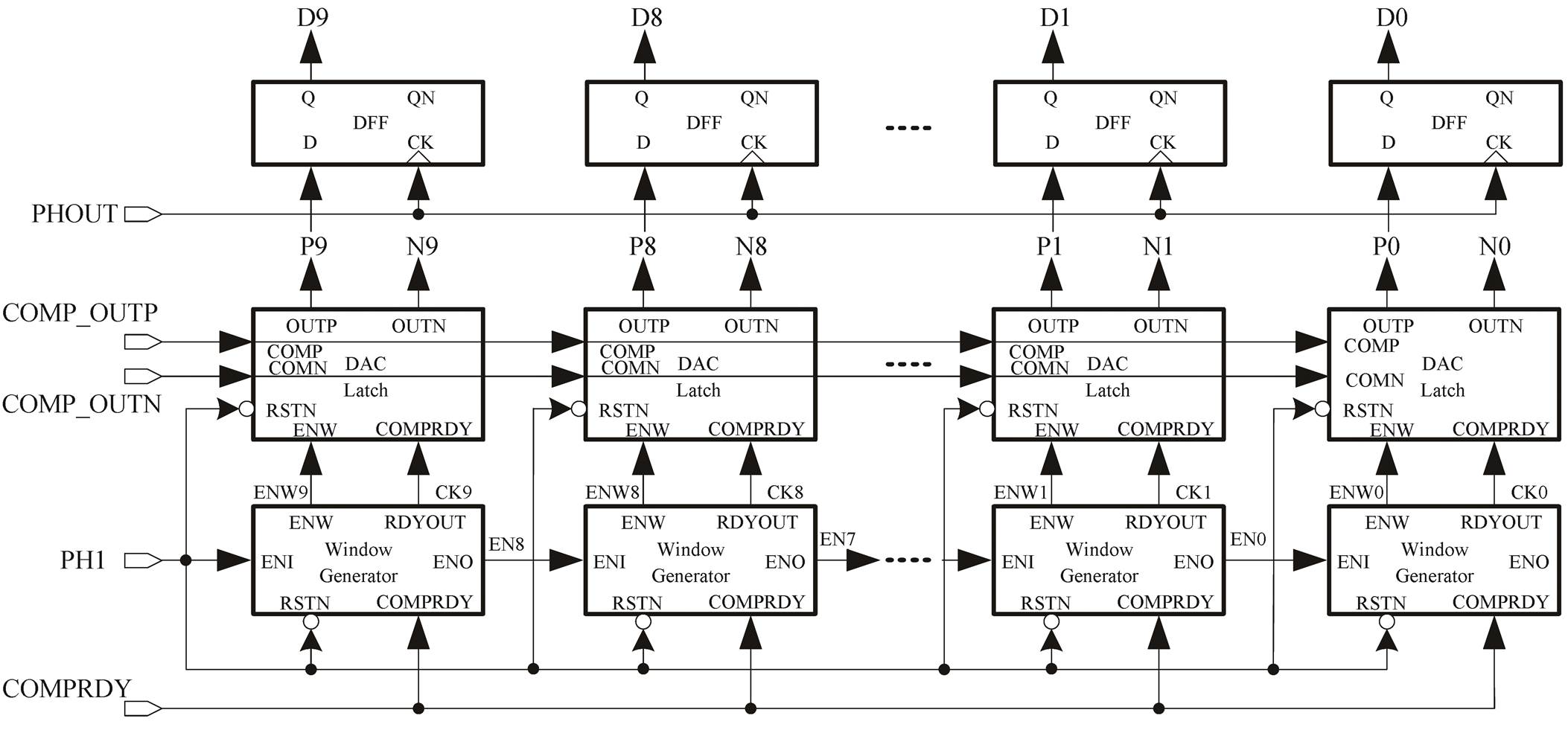

SAR ADC 的转换速率主要由两个环路的延迟时间决定: 一个环路是比较器输出经过锁存并传输至DAC的电容控制开关, 使得 DAC 根据上一次的比较结果产生新的输出电压, 称为 DAC 环路; 另一 个环路是比较器产生比较结果后重新复位的再生环路, 称为比较器环路。进行电路设计时, 在尽量缩短上述两个环路延迟时间的同时, 需要确保比较器再次进行比较之前 DAC 环路已经完成输出电压的更新。本文设计的 DAC 环路采用开窗逻辑[12], 该逻辑可以在比较器产生输出时, 直接将比较结果传输至 DAC 的控制开关, 可大大缩短 DAC 环路的延迟时间, 而传统寄存器型的 SAR 逻辑则需要经过两个寄存器的上升延时。利用开窗逻辑实现的 SAR逻辑见图7。

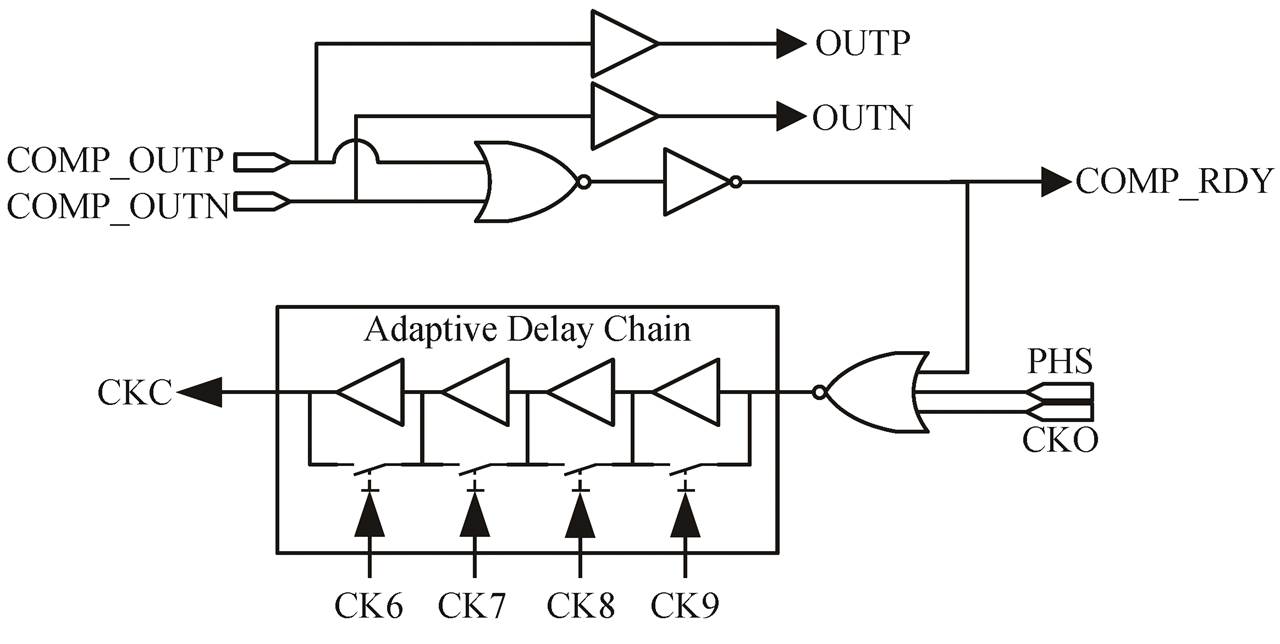

DAC环路的延迟时间由逻辑延时和DAC电压建立时间两部分组成。逻辑延时是固定的, DAC电压建立时间则与电容大小成正比, 会随着 ADC 的转换过程递减。因此, 本文设计的比较器环路延时是一个受 ADC 输出比特控制的自适应延时链, 如图 8 所示。自适应延时链的设计也体现了全异步SAR 逻辑的思想。

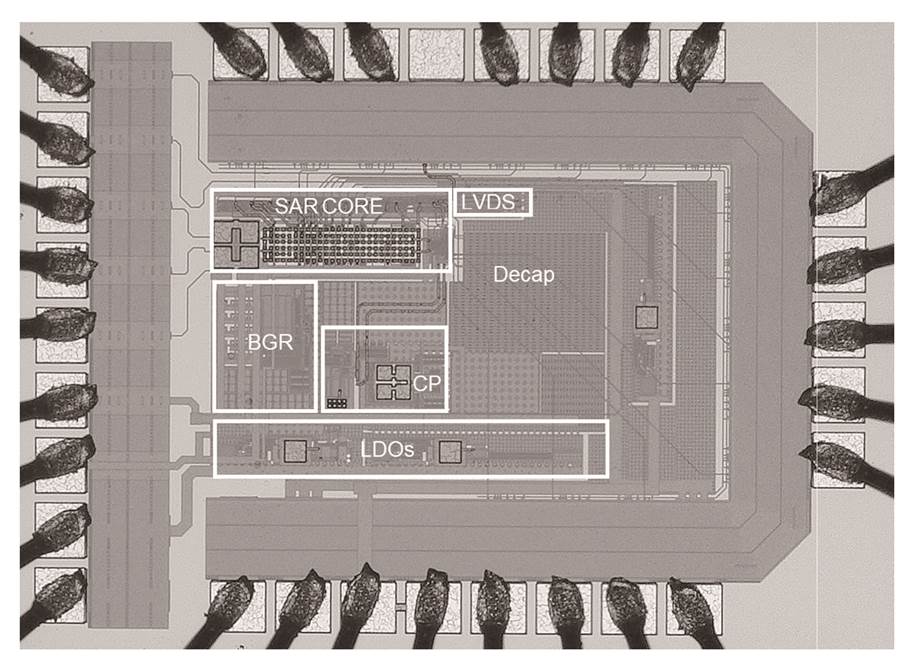

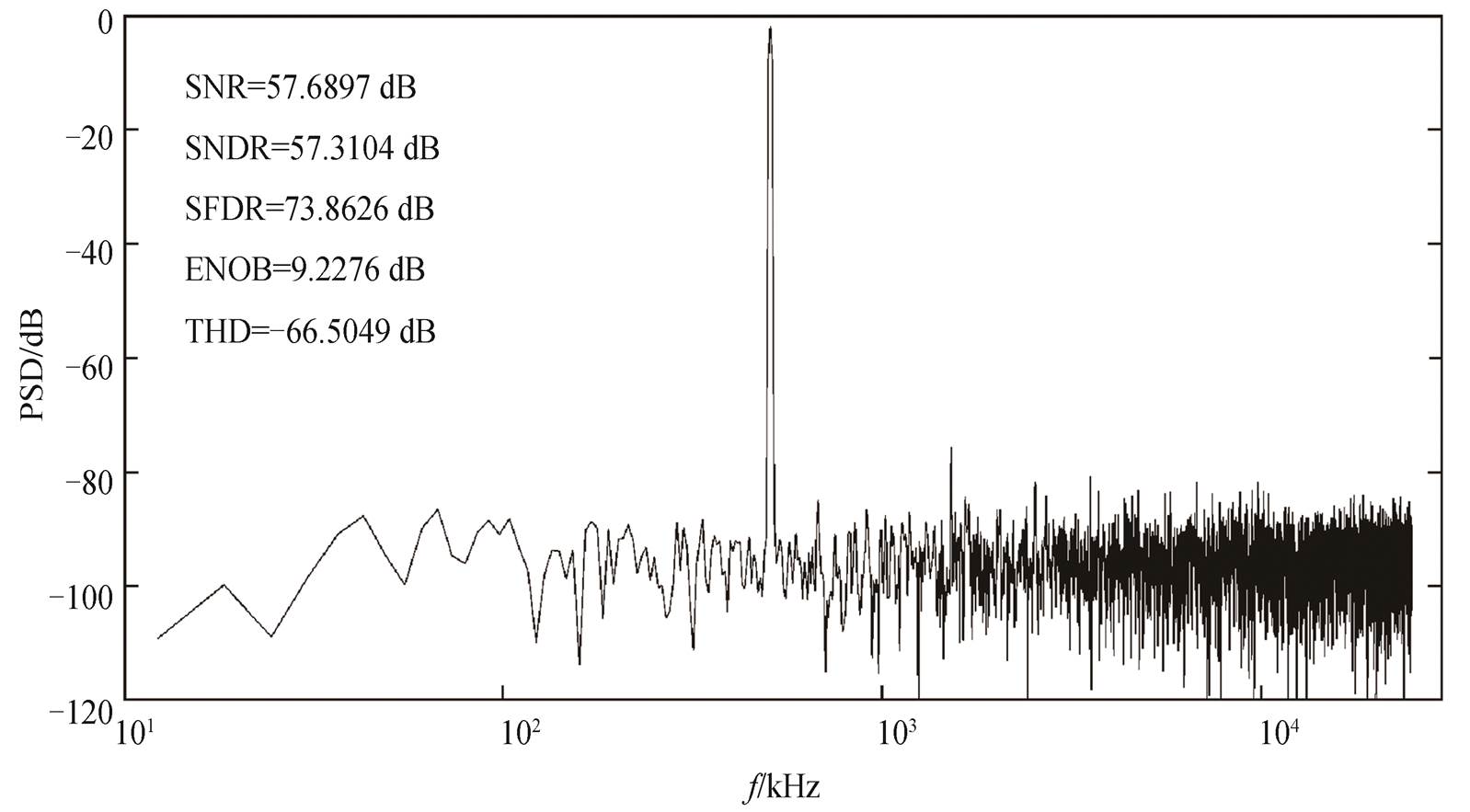

图 9 为本文流片得到的 SAR ADC 芯片照片, SAR ADC的面积为 340 μm×110 μm, 测试结果显示, 当 ADC 工作频率为 50 MHz时, 电源的平均电流为 1.8 mA。当输入信号的频率为 506.6 kHz, 幅度为–1.58 dBFs时, SAR ADC 输出信号的频谱如图10 所示, 通过 MATALB 计算可知, 此时 ADC 的SNDR 为 57.31 dB, 可以实现 9.23-bit 的有效模数转换, ADC 的 SFDR 为 73.86 dB。为了减小 ADC对时钟信号的干扰, 芯片采用LVDS的时钟输入。

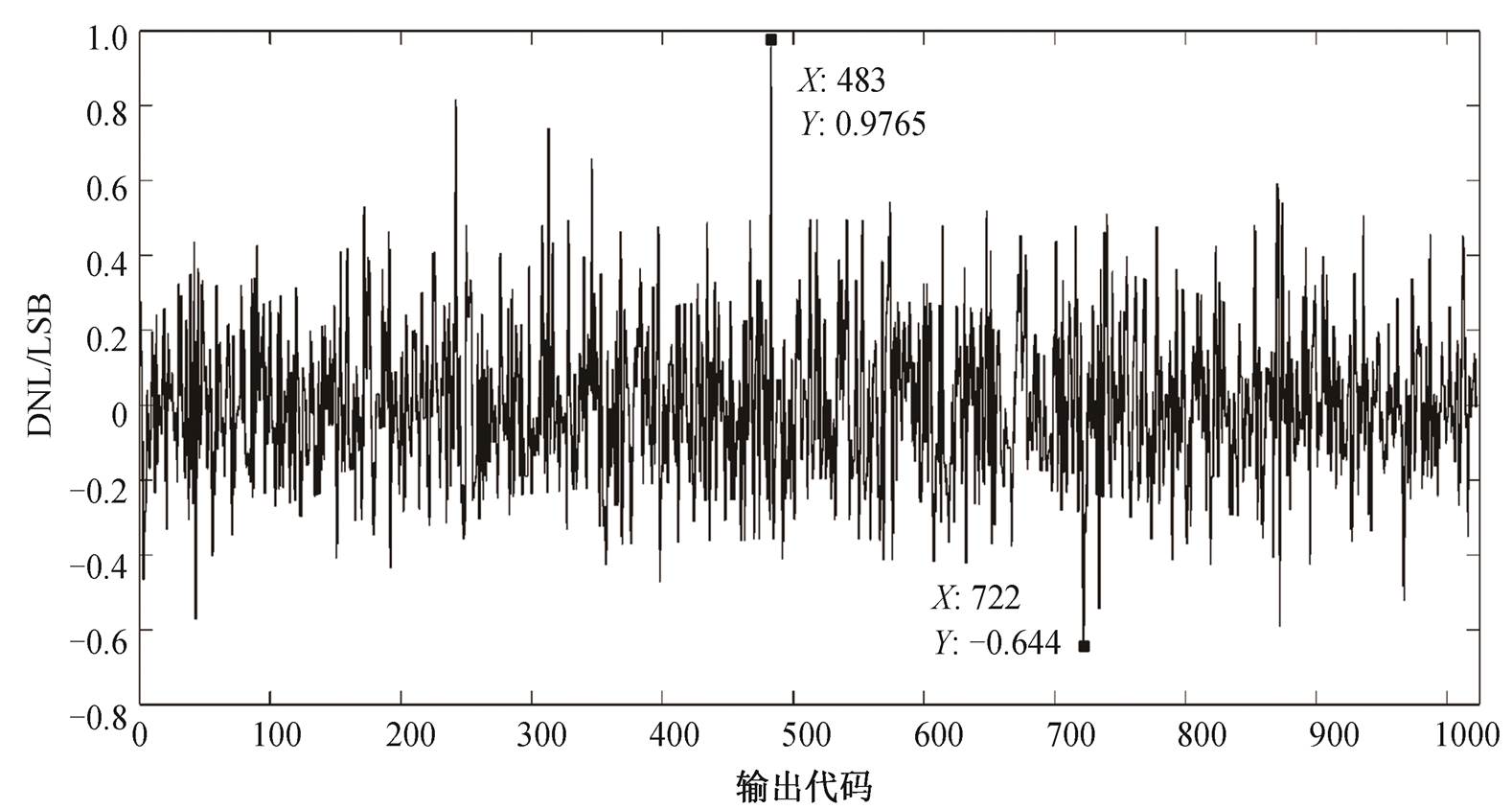

图 11 和 12 分别是 SAR ADC 的 INL 和 DNL的测试结果。可以看出, SAR ADC 的 INL 为 1.81 LSB/–1.58 LSB, DNL为0.98 LSB/–0.64 LSB。ADC的静态非线性性能欠佳, 初步分析其原因, 是由于 DAC 的电容阵列及其走线对称性存在缺点, 将来需要重新对版图进行改善。

图7 开窗模式的SAR逻辑

Fig. 7 Open windows SAR logic

图8 本文提出自适应延时比较器环路

Fig. 8 Proposed adaptive delay comparator loop

图9 SAR ADC芯片照片

Fig. 9 Chip photograph of SAR ADC

图10 SAR ADC的FFT分析结果

Fig. 10 FFT result of the prototype SAR ADC

图11 SAR ADC的INL分析结果

Fig. 11 INL result of the prototype SAR ADC

本文提出一种混合电容切换逻辑, 基于该切换逻辑设计的电荷重分配型 SAR ADC 无需任何额外的稳压电源和电容补偿阵列, 即可实现比较器输入共模电压的稳定, 因此可以降低 ADC 芯片的面积和功耗。通过芯片的仿真和测试, 对本文提出的电容切换逻辑进行了验证。在稳定比较器输入共模电压的基础上, 今后将继续对 SAR 锁存逻辑进行研究, 降低比较器输出值 DA 输入之间的传输延时, 进一步提高ADC的转换速率。

图12 SAR ADC的DNL分析结果

Fig. 12 DNL result of the prototype SAR ADC

参考文献

[1]Xing Dezhi, Zhu Yan, Chan Chi-Hang, et al. Seven-bit 700-MS/s four-way time-interleaved SAR ADC with partial Vcm-based switching. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2017, 25(3): 572–583

[2]Lim Y, Flynn M P. A 1 mW 71.5 dB SNDR 50 MS/s 13 bit fully differential ring amplifier based saras-sisted pipeline ADC. IEEE J Solid-State Circuits, 2015, 50(12): 2901–2911

[3]Molaei H, Khorami A, Eslampanah S M S. et al. A four bit low power 165 MS/s flash-SAR ADC for sigma-delta ADC application// IEEE International Conference on Electronics, Circuits, and Systems (ICECS). Cairo, 2015: 153–156

[4]Liu C C, Chang S J, Huang G Y, et al. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J Solid-State Circuits, 2010, 45(4): 731–740

[5]Wang Hao, Zhu Zhangming. Energy-efficient and reference-free monotonic capacitor switching scheme with fewest switches for SAR ADC. IEICE Electro-nics Express, 2015, 12(7): 1–5

[6]Chen L, Sanyal A, Ma J, et al. Comparator common-mode variation effects analysis and its application in SAR ADCs // IEEE ISCAS. Montréal, 2016: 2014–2017

[7]Song H, Leea M. Asymmetric monotonic switching scheme for energy-efficient SAR ADC. IEICE Elec-tronics Express, 2014, 11(12): 1–5

[8]Shahmohammadia M, Ashtiani S J. Energy and area-efficient tri-level switching procedure based on half of the reference voltage for SAR ADC. IEICE Elec-tronics Express, 2012, 9(17): 1397–1401

[9]Zhang Y, Chen H, Guo G, et al. Energy-efficient hybrid split capacitor switching scheme for SAR ADCs. IEICE Electronics Express, 2016, 13(7): 1–5

[10]Zhu Y, Chan C H, Chio U F, et al. A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. IEEE J Solid-State Circuits, 2010, 45(6): 1111–1121

[11]Lu Y, Sun L, Li Z, et al. A single-channel 10-Bits 160 MS/s SAR ADC in 65 nm CMOS. Journal of Semi-conductor, 2014, 35(4): 045009-1-8

[12]Lü W, Luo D, Mei F, et al. A 0.6 V 10 bit 1 MS/s monotonic switching SAR ADC with common mode stabilizer in 0.13 μm CMOS. Journal of Semicon-ductor, 2014, 35(5): 055006-1-7

A Design of 10B SAR ADC with Novel Mixed-Monotonic Capacitor Switching Scheme

GE Binjie, LI Yan†, YU Hang, FENG Xiaoxing

College of Computer Science & Software Engineering, Shenzhen University, Shenzhen 518060; † Corresponding author, E-mail: liyan@szu.edu.cn

Abstract A mixed-monotonic capacitor switching scheme which can provide stable common-mode voltage (Vcm) without any additional voltage regulator and compensation capacitor array is proposed for the successive approximation register (SAR) analog-to-digital (ADC). The proposed scheme contains two equal amplitude but opposite monotonicity switched capacitor arrays, the stabilization of the common mode voltage is achieved with self-complementation of the differential voltage. Based on this technique, a 10-bit 50MS/s prototype is designed in CMOS 0.18 μm technology. A window opening SAR logic is used to reduce the transmission time from the comparator out to DAC control signal. An adaptive delay chain is used in the comparator loop to reduce the conversion time of lower bit in the SAR ADC. Measurement result shows that the SAR ADC can achieve a SNDR equal to 57.31 dB, and INL and DNL are equal to 1.81 LSB and 0.98 LSB respectively.

Key words mixed-monotonic capacitor switching; Vcm-stablized; SAR ADC

中图分类号 TN432

doi: 10.13209/j.0479-8023.2018.048

国家自然科学基金(61471245, U1201256)、广东省省级科技计划项目(2014B090901031)和深圳市科技计划项目(JCYJ20160308095019383, JSGG20150529160945187)资助

收稿日期: 2017–08–24;

修回日期: 2017–12–07;

网络出版日期: 2018–09–03